논리 설계를 어느정도 배우고 나면 이제 논리식에 맞게 게이트를 조합한 회로를 직접 그려서 설계하지 않고도 HDL(Hardware Description Language; 하드웨어 기술언어)를 이용하여 좀 더 추상적으로 설계할 수 있는 방법을 배운다.

Fundamentals of Logic Design, 7/e (ISBN 9781133628484)

에서는 VHDL(Very High Speed Integrated Circuit HDL)을 다룬다.

실습 환경

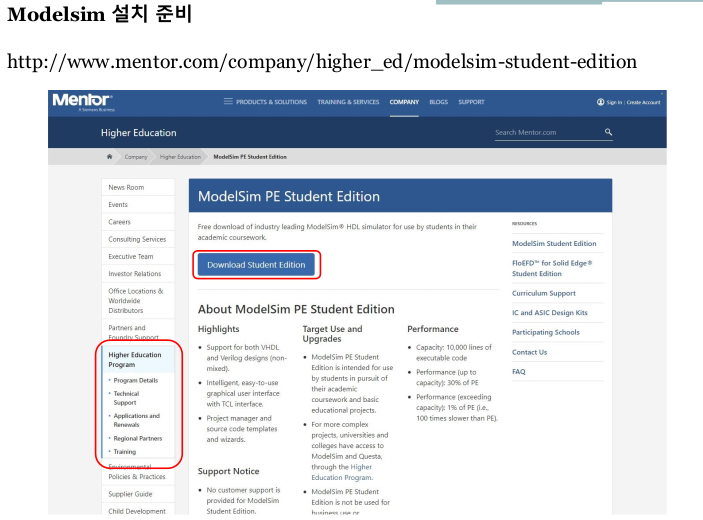

1. ModelSim (Mentor)

강의 자료에 Mentor의 modelsim을 사용하라길래 가봤더니…

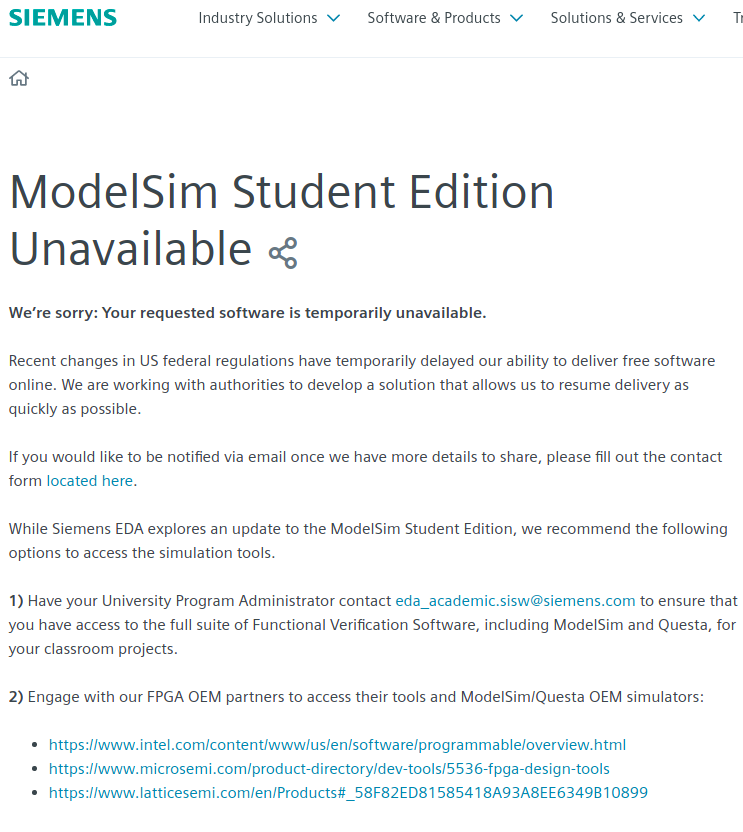

…?

2021년 1월 멘토사가 지멘스사에 인수되어 지멘스 EDA로 바뀌었는데, 상기 서술된대로 최근 변경된 연방법에 의해 일시적으로 배포를 연기하고 있는데, intel이나 microsemi등 파트너 FPGA OEM사의 modelsim 툴을 이용할 수 있도록 안내하고 있다.

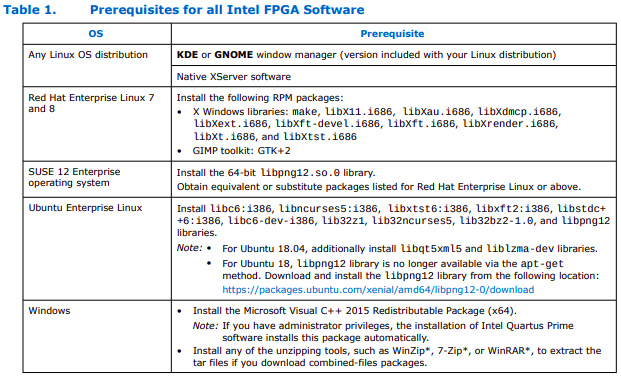

2. ModelSim - Intel FPGA Edition

Intel FPGA 회원가입 후 Quartus Prime Lite Edition 링크에서 ModelSim Intel Edition을 다운로드 받을 수 있다. 그런데…

대충봐도 의존성 문제가 발목을 잡을 것처럼 보인다. 몇몇 패키지를 비롯해 libpng12 패키지는 deprecated 되어 apt를 통해 설치할 수 없다.

윈도우에서는 Visual C++ 2015 재배포가능 패키지가 자동으로 설치되니까 사실 편한데… 저장공간 파티션 문제도 있고 프로그램 사용을 위해 매번 왔다갔다 하는 건 불편할 것 같아서, 최후의 수단으로 남겨놓고 다른 방법을 찾아보기로 했다.

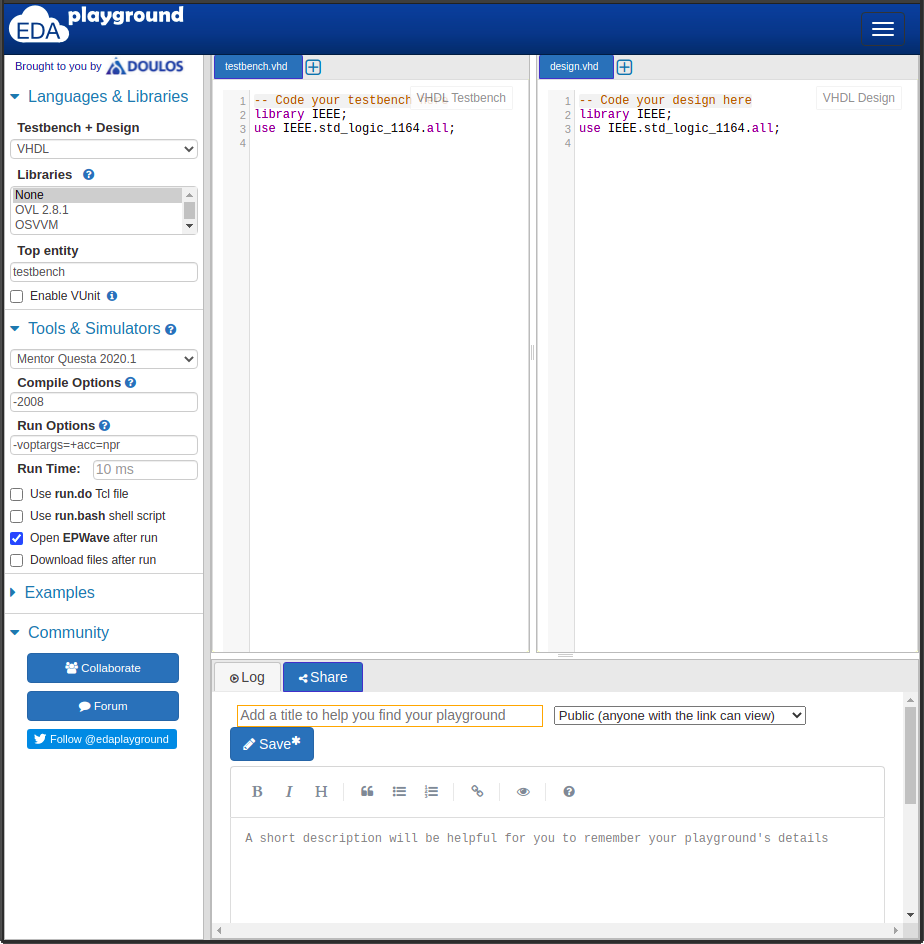

3. EDA Playground

EDA Playground 웹사이트에서 VHDL을 비롯해 Verilog나 SystemC 등 하드웨어 기술언어로 작성 후 여러 상용 컴파일러로 컴파일하고 시뮬레이터로 확인할 수 있다.

추가 패키지 설치, 환경설정도 필요없고 다양한 언어, 컴파일러를 지원해 쉽게 사용할 수 있어서 종종 사용하게 될 것 같다.

다만 웹페이지 상의 텍스트 에디터만을 사용하는 게 아무래도 불편하긴하기도 하고, 그렇닥 그걸 매번 복사하고 붙여넣을 생각을 하면 피하고 싶긴 하다. 작성한 파일을 서버에 저장하고 관리할 수 있긴하지만 아무래도 파일을 직접 저장하고 싶어서 다른 방법을 찾아봤다.

4. GHDL + GTKWAVE + VSCODE

GHDL은 오픈소스 VHDL 87/93/08 Compiler/Simulator이다. 컴파일 후 vcd파일로 출력하면 이를 GTKWave와 같은 Wave Analyzer로 볼 수 있다.

VS Code와 함께 아래와 같은 extension들도 있어 편리한 환경을 구성할 수 있을 것 같았다.

GHDL+GTKWAVE+VSCode 개발환경 구성하기

GHDL

apt 저장소에도 GHDL이 등록되어 있으나 0.3.7 버전이고, 현재 1.0.0을 출시했다. GHDL git repository release에서 다운로드 받거나 ghdl.git을 clone하면 최신 버전을 사용할 수 있다.

소스를 받으면 빌드후 설치를 해야하는데 README에도 자세한 설명이 없어서 좀 헤맸다. ghdl 공식 문서와 stackoverflow를 참고하였다.

$ git clone https://github.com/ghdl/ghdl.git

$ sudo apt install gnat

$ cd ghdl

$ mkdir build

$ cd build

$ ../configure --prefix=/usr/local

$ make

$ sudo make install

현재 GHDL은 gcc뿐 아니라 gnat에도 의존성을 가지고 있다. build 결과물이 상위 디렉토리 내용물과 섞이면 난잡해지므로 build 디렉토리를 만들어 따로 빌드후 설치하였다.

GTKWAVE

vcd 시뮬레이터 파일을 열기 위해 아래와 같이 gtkwave도 설치한다.

$ sudo apt install gtkwave

이제 아래와 같이 명령줄을 입력하여 컴파일 후 시뮬레이션파일을 출력, 확인할 수 있다.

$ ghdl -a design.vhd

$ ghdl -a testbench.vhd

$ ghdl -e TestBench

$ ghdl -r TestBench --vcd==TestBench.vcd

$ gtkwave TestBench.vcd

VSCODE w/ extensions

VSCode는 마켓플레이스에 정말 많은 extension을 가지고 있다! vscode는 텍스트 편집기에 터미널, git과 몇가지 자잘한 기능들은 붙여놓았을 뿐이지만 extension으로 확장되면 정말 강력해진다.

VHDL Extension을 설치하면 .vhdl, .vhd등 VHDL 파일을 인식하고 syntax highlighting, code snippet, code complition, brace matching등의 편리한 기능들이 제공된다.

VHDL에는 Indent, Space sensitive는 아니지만 들여쓰기는 가독성에 큰 차이를 준다. 익숙치 않아서인지 edaplayground의 반쪽짜리 formatting이 불편했는데 VHDL Formatter Extension을 사용해서 좀 더 일관되고 깔끔한 formatting이 가능해졌다.

WaveTrace Extension를 통해 gtkwave없이 vscode 내에서 vcd 파일을 열어볼 수 있다.

makefile

단순해서 design파일과 그의 testbench파일 하나만 있을때야 괜찮은데, 파일이 여러 개가 되면 조금씩 부담스러워진다.

게다가 ghdl 기본 옵션이 VHDL93이기 때문에 VHDL08로 컴파일 하기 위해서는 --std=08옵션을 추가해야한다. 모든 명령에 같이 넣어줄 생각을 하면 여간 불편한 일이 아니다. 역시 빌드자동화 도구가 힘을 발휘할 때다.

GHDL = ghdl

WAVE = gtkwave

STD = --std=08

SRCS = $(notdir $(wildcard *.vhd))

TARGET = TestBench

STOP = --stop-time=32ns # Set time to stop (Leave it empty if unnecessary)

$(TARGET).vcd: $(SRCS)

$(GHDL) -a $(STD) $(SRCS)

$(GHDL) -e $(STD) $(TARGET)

$(GHDL) -r $(STD) $(TARGET) --vcd=$(TARGET).vcd $(STOP)

wave: $(TARGET).vcd

$(WAVE) $(TARGET).vcd

clean:

rm *.cf $(TARGET).vcd

컴파일러 GHDL과 Wave Analyzer gtkwave를 변수로 만들었다.

vhdl standard도 변수로 빼놓아 필요할 때 편리하게 바꿀 수 있도록 작성했고, target이름도 정할 수 있다.

$(STOP)을 통해 simulation 시간을 제한할 수 있다. testbench architecture내 모든 process가 wait; 으로 멈추거나, std.env.finish, std.env.stop등으로 멈추는 것이 아닌 이상 해당 변수를 이용해 testbench가 무한히 돌지 않도록 설정해 줄 필요가 있다.

.vhd 파일들을 wildcard를 이용해 $(SRCS)로 참조할 수 있도록 하였다.

make 명령어를 통해 컴파일, 시뮬레이션 후 $(TARGET).vcd 파일을 출력하도록 해 놓았고, $(SRCS)에 의존하므로 소스가 바뀌면 다시 컴파일 및 시뮬레이션 한다.

make wave 명령어를 통해 시뮬레이션을 통해 출력된 $(TARGET).vcd 파일을 gtkwave를 통해 열어볼 수 있다. $(TARGET).vcd에 의존하므로 소스가 변경된 이후 컴파일/시뮬레이션 되지 않았다면 컴파일/시뮬레이션이 이루어진 후 gtkwave가 실행된다.

make clean 명령어로 컴파일 과정에서 생성된 .cf파일과 시뮬레이션 후 출력인 $(TARGET).vcd를 제거할 수 있다.

xilinx ise, vivado나 다른 modelsim 등 대체수단을 알아봤었지만, 다들 무겁고 많은 저장공간을 차지해서 GHDL+GTKWAVE+VSCode 개발환경에 정착하기로 했다. 물론 시뮬레이션이 전부가 아니고 언젠가 FPGA 보드에 직접 업로드하는 날도 올텐데, 그건 그 때일이고… 그때 쯤 되면 좋은 컴퓨터를 새로 사겠지…